IAR Embedded Workbench for RISC-V

Complete development toolchain providing one toolbox in one view, giving you one uninterrupted workflow. As a well established frontrunner in the embedded industry, you can rely on IAR Embedded Workbench to compile, analyze and debug your code in the most efficient way.

01

Highly optimizing compiler technology

IAR Embedded Workbench offers excellent optimization technology to ensure developers that the application fits the required needs and optimizes the utilization of on-board memory and necessary speed.

02

Broad device support

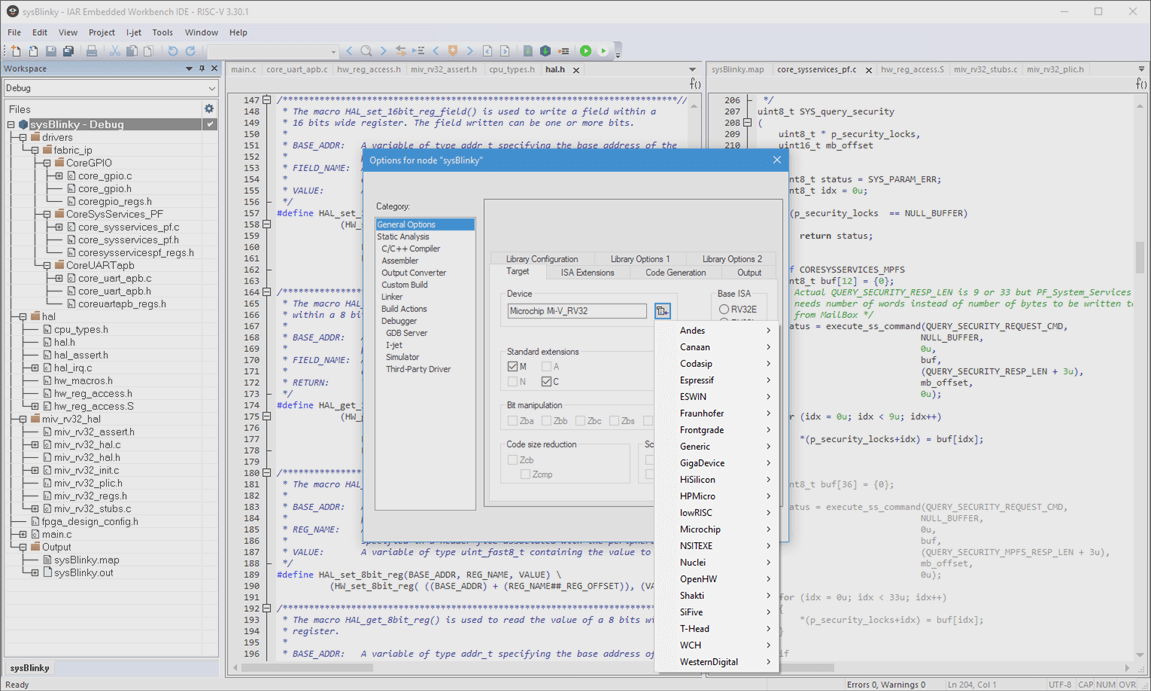

Supporting 32-bit RV32E and RV32I cores, as well as 64-bit RV64I cores. RISC-V extensions such as the C extension (compressed instructions), F and D (32- and 64-bit FPU), M (integer multiplication and division), A (Atomic), and the standardized parts of B (bit manipulation) are also supported, together with the Andes DSP and Performance extensions.

03

Comprehensive debugger

The C-SPY Debugger provides extensive debugging capabilities, giving full control of the application in real time. Native debug probe support through I-jet enables high-speed in-circuit debugging and SMP multicore debugging. For livestreaming of trace information for code coverage and profiling purposes, the trace probe I-jet Trace is supported. In addition, a plugin SDK is available for easy integration of emulator interfaces, RTOSs, TCP/IP and network stacks, etc.

04

Technical support included

As the leading commercial tools supplier for RISC-V, we are able to provide worldwide technical support with our products. With a Support and Update Agreement, you also get immediate access to the latest updates and features.

05

On-demand training included

When you buy a license of IAR Embedded Workbench for RISC-V, you get access to free training courses through our IAR Academy on Demand offering.

Product overview

See latest version of IAR Embedded Workbench for RISC-V in action and learn how to get started with the toolchain in this video.

Latest releases

We are constantly updating and refining our tools with new features, new device support and extended capabilities.

Latest version 3.30

- Scalar Cryptography (Zkn, Zks) Instruction Set

Extensions

The Zkn and Zks RISC-V extensions implement Scalar Cryptography instructions aimed at accelerating the NIST and ShangMi cryptographic standards, respectively. - Code Size Reduction (Zcb, Zcmp) Instruction Set

Extensions

The Zcb standard extension provides compressed variants of a number of existing extensions. The Zcmp extension is a set of instructions (including push/pop) that can be executed as a series of existing 32-bit RISC-V instructions. - Improved code generation for the Bitmanip extensions

- Optimized ceil, floor, and round libraries for soft-float and Zfinx

- Support for misaligned data access

- New compiler GCC extensions

- IDE Build Actions improvements

Build actions replace the previous pre- and post-build actions with a more intuitive mechanism, to which multiple actions can be executed before compilation and before/after linking. - Breakpoints

Breakpoints can now be set during application execution, even when there is no hardware support for it. - New devices

Version: 3.20

Zfinx and Zdinx standard RISC-V extensions

- Support for standard extensions for Floating-Point in Integer Registers.

CMO standard RISC-V extensions

- Support for the Cache Management Operations (CMO) extensions Zicbom, Zicboz, and Zicbop.

Auto compressing Assembler

- When support for the C extension is enabled, the assembler automatically converts normal instructions to compressed instructions.

Optimized ceil, floor, and rounding library functions

Improvements for the Andes performance extension on RV64

Improved code generation for the Bitmanip extensions

Asymmetric multicore debugging improvements

- It is now possible to perform multi-architecture AMP debugging using two IAR Embedded Workbench instances installed in separate directories. The IAR Embedded Workbench instances no longer have to be installed in the same directory.

Support for Nexus serial trace

- With an I-jet Trace probe, it is now possible to enable serial trace (serial pin).

New devices

- Sifive

E6-A - Nuclei

NA900 - Frontgrade

Gaisler

GP32L-SC

GP64L-SC

MC32L-SC

MC64-SC

Version: 3.11

- Andes CoDense extensions

Andes V5 architecture code density enhancement, to reduce program code size - P extension support

Standard Extension for Packed-SIMD Instructions, updated to 0.9.11 - Debugger enhancements

GDB server improvements – more debug server variants supported

SMP and AMP multicore debugging improvements - Editor enhancements

Window color themes – dark mode improvements - Visual Studio Code extensions

The IAR Build and IAR C-SPY Debug extensions available on Microsoft Marketplace enable you to work in Visual Studio Code (with IAR Embedded Workbench installed) to:

- Build IAR Embedded Workbench projects

- Run the C-STAT static analysis tool

- Debug applications using the same range of hardware/debug probes as in IAR Embedded Workbench - New devices

Version: 3.10

64-bit RISC-V core support

- Support for RV64 RISC-V cores and the RV64I base instruction set

- Support for RV64 devices from Andes, Codasip, Microchip, Nuclei and SiFive

Library support for the C++17 language standard

- The toolset now includes a new C++ library that supports C++17 library features.

Debug enhancements

- RV64 core debug support

- SMP multicore debug support for I-jet

Editor enhancements

- Window color themes - dark mode

- Gray out inactive code

What type of license do you need?

Our tools are available in a flexible license model to suit your company needs. Together with our support and update agreements, you get the support you need in multiple time zones and multiple languages. Send a request for quote or contact sales to get started.

Stand-alone

- Personal license

- Locked to a specific PC

- Works without network connection

Mobile

- Personal license with flexibility

- Locked to a USB dongle

- Works without network connection

- Protects license from hardware failure

Want to know more about IAR Embedded Workbench for RISC-V?

We are available to answer any questions about our products. To help you make the most out of your experience, you can also find plenty of information in our Learn section and at the customer portal My Pages.

Add-ons and integrations

IAR Embedded Workbench for RISC-V provides several integrated tools to help you succeed in your development projects.

Get quote

Want to use this product in your development projects? Our sales team is here to guide you to the right solution. Complete this form, and we will get back to you with a price quote tailored to your needs.

Related products

User guides and documentation

Languages and standards

The IAR C/C++ compilers offer different dialects of the C and C++ programming languages, as well as different extensions specific for embedded programming (please note that not all language standards are supported for all target implementations). The compiler can be instructed to disable extensions for strict conformance to the standards.

A wide range of industry-standard debug and image formats compatible with most popular debuggers and emulators are supported. This includes ELF/DWARF where applicable.

ISO/ANSI C/C++ Compliance

The IAR C/C++ compilers adhere to a freestanding implementation of the following C programming language standards:

- INCITS/ISO/IEC 9899:2018, known as C18 (Latest version only).

- The compiler supports all C++17 features. The C++ library supports C++14 with no C++17 additions. (Latest version only).

- ISO/IEC 14882:2015, known as C++14

- INCITS/ISO/IEC 9899:2012, known as C11

- ANSI X3.159-1989, known as C89

The ISO/ANSI C/C++ Compliance level varies between the different compilers. For complete information, please refer to the IAR C/C++ Compiler user documentation in your chosen product.

IEEE 754 standard

IAR Embedded Workbench supports the IEEE 754 standard for floating-point arithmetic.

MISRA C

MISRA C is a software development standard for the C programming language developed by MISRA, The Motor Industry Software Reliability Association. Its aims are to facilitate code safety, portability and reliability in the context of embedded systems, specifically those systems programmed in ISO C.

The first edition of the MISRA C standard, "Guidelines for the use of the C language in vehicle based software", was produced in 1998. In 2004, a second edition was produced with many substantial changes to the guidelines, including a complete renumbering of the rules. Additionally MISRA C:2012 with extended support and MISRA C++:2008 for identifying unsafe code constructs in the C++ standard have also been added to the standards.

IAR Embedded Workbench features an add-on product C-STAT so you can check compliance with rules as defined by MISRA C:2004, MISRA C++:2008 and MISRA C:2012.

Test validation

We use the following commercial test suites to test conformance of our tools to the standards:

- Plum Hall Validation test suite for ISO/IEC C conformance

- Perennial EC++ Validation Suite for C++ conformance

- Dinkum C++ Proofer to test how our libraries conform to the C and C++ standard as well as test our STL implementation against the C++ standard.

In addition to the commercial suites, we use several in-house test suites for testing new features, regression testing, corrected errors, etc.